Tei-Wei Kuo Edwin Sha Minyi Guo Laurence T. Yang Zili Shao (Eds.)

# LNCS 4808

# Embedded and Ubiquitous Computing

International Conference, EUC 2007 Taipei, Taiwan, December 2007 Proceedings

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Tei-Wei Kuo Edwin Sha Minyi Guo Laurence T. Yang Zili Shao (Eds.)

# Embedded and Ubiquitous Computing

International Conference, EUC 2007 Taipei, Taiwan, December 17-20, 2007 Proceedings

Volume Editors

Tei-Wei Kuo National Taiwan University Taiwan 106, Republic of China E-mail: ktw@csie.ntu.edu.tw

Edwin Sha University of Texas at Dallas Richardson, TX 75083-0688, USA E-mail: edsha@utdallas.edu

Minyi Guo The University of Aizu Aizu-Wakamatsu City, Japan E-mail: minyi@u-aizu.ac.jp

Laurence T. Yang St Francis Xavier University Antigonish, NS, B2G 2W5, Canada E-mail: ltyang@gmail.com

Zili Shao The Hong Kong Polytechnic University Hung Hom, Kowloon, Hong Kong E-mail: cszlshao@comp.polyu.edu.hk

Library of Congress Control Number: 2007940386

CR Subject Classification (1998): C.2, C.3, D.4, D.2, H.4, H.3, H.5, K.4

LNCS Sublibrary: SL 3 – Information Systems and Application, incl. Internet/Web and HCI

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-77091-7 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-77091-6 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© IFIP International Federation for Information Processing 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, IndiaPrinted on acid-free paperSPIN: 1219966206/31805 4 3 2 1 0

#### Preface

It has been widely recognized that embedded and ubiquitous computing will have tremendous impacts on many aspects of our daily life. Innovation and close collaboration between academia and industry are the keys to guaranteeing success in the development and deployment of the technology in embedded and ubiquitous computing.

The IFIP International Conference on Embedded and Ubiquitous Computing (EUC) provides a forum for engineers and scientists in academia, industry, and government to address challenges and to present and discuss their ideas, results, work in progress and experience. The Technical Program Committee (TPC) of EUC 2007 was lead by the TPC Chair, Tei-Wei Kuo, and TPC Vice Chairs. A strong international TPC was formed to review and evaluate the submissions. Each paper was reviewed carefully by at least three TPC members or external reviewers. It was extremely difficult for the TPC to select the presentations because there were so many excellent and interesting submissions. There were 217 submissions from all over the world, and only 65 papers are published in this proceedings volume.

We wish to thank the PC members for the time and thought that they gave in creating the excellent program. We also want to thank all of the authors who submitted their papers and made this conference a success. We are also grateful to the Organizing Committee in organizing the conference, and to the keynote speakers who agreed to give exciting speeches. Special thanks also go to Edwin Sha, the General Chair, for his excellent leadership, Zili Shao, Chi-Sheng Shih, Mieso Denko, Shih-Hao Hung, Chia-Lin Yang, Tai-Yi Huang, Chih-wen Hseuh, Morris Chang, Zhen Liu, Agustinus Borgy Waluyo, and Shi-Wu Lo for all the excellent work in the conference organization.

September 2007

Tei-Wei Kuo Edwin Sha Laurence T. Yang Minyi Guo Zili Shao

# Organization

EUC 2007 was organized and supported by the International Federation for Information Processing (IFIP). It was held in cooperation with the National Taiwan University and (LNCS) of Springer.

#### **Orgnizing Committee**

| Honoraray Chair     | Si-Chen Lee, National Taiwan University, Taiwan                                                                                                                |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Chair       | Edwin Sha, University of Texas at Dallas, USA                                                                                                                  |

| Program Chair       | Tei-Wei Kuo, National Taiwan University, Taiwan                                                                                                                |

| Program Vice Chairs | Li-Pin Chang, National Chiao-Tung University,<br>Taiwan                                                                                                        |

|                     | X. Sharon Hu, University of Notre Dame, USA                                                                                                                    |

|                     | Jinsoo Kim, KAIST, Korea                                                                                                                                       |

|                     | Dongsheng Wang, Tsinghua University, China                                                                                                                     |

|                     | Hiroyuki Tomiyama, Nagoya University, Japan                                                                                                                    |

|                     | Samarjit Chakraborty, National University of                                                                                                                   |

|                     | Singapore, Singapore                                                                                                                                           |

|                     | Yu-Chee Tseng, National Chiao-Tung University,                                                                                                                 |

|                     | Taiwan                                                                                                                                                         |

|                     | Nicolas Navet, INRIA Lorraine, France                                                                                                                          |

|                     | I-Ling Yen, University of Texas at Dallas, USA                                                                                                                 |

|                     | Cho-Li Wang, University of Hong Kong, Hong Kong                                                                                                                |

|                     | Mohan Kumar, University of Texas at Arlington,<br>USA                                                                                                          |

|                     | Ai-Chung Pang, National Taiwan University, Taiwan                                                                                                              |

|                     | Joseph Ng, Hong Kong Baptist University, Hong Kong                                                                                                             |

|                     | Jiman Hong, Soongsil University, Korea                                                                                                                         |

| Steering Committee  |                                                                                                                                                                |

| Chairs              | Minyi Guo, University of Aizu, Japan                                                                                                                           |

|                     | Laurence Yang, St. Francis Xavier University, Canada                                                                                                           |

|                     | Jane Liu, National Taiwan University and Academia<br>Sinica, Taiwan                                                                                            |

| Local Organizing    |                                                                                                                                                                |

| Chairs              | Chia-Lin Yang, National Taiwan University, Taiwan                                                                                                              |

|                     | Chih-Wen Hsueh, National Taiwan University, Taiwan                                                                                                             |

| Registration and    |                                                                                                                                                                |

| Finance Chairs      | Tai-Yi Huang, National Tsing Hua University, Taiwan<br>Shih-Hao Hung, National Taiwan University, Taiwan<br>Shi Wu Lo, National Chung Chong University, Taiwan |

|                     | Shi-Wu Lo, National Chung-Cheng University, Taiwan                                                                                                             |

| Workshop Chairs    | Mieso Denko, University of Guelph, Canada               |

|--------------------|---------------------------------------------------------|

|                    | Chi-Sheng Shih, National Taiwan University, Taiwan      |

| Panel Chair        | Ted Chang, Quanta Computer Inc., Taiwan                 |

| Publicity Chairs   | Morris Chang, Iowa State University, USA                |

|                    | Zhen Liu, Nagasaki Institute of Applied Science,        |

|                    | Japan                                                   |

|                    | Agustinus Borgy Waluyo, Monash University,<br>Australia |

| Publication Chairs | Zili Shao, Hong Kong Polytech University, Hong Kong     |

|                    | Chi-Sheng Shih, National Taiwan University, Taiwan      |

| Keynote            | Dr. L.G. Chen, National Taiwan University, Taiwan       |

|                    | Dr. Wei Zhao, Rensselaer Polytechnic Institute, USA     |

#### **Technical Committee**

| Real-Time/Embedded<br>Operating Systems | Li-Pin Chang, National Chiao-Tung University,<br>Taiwan                   |  |  |

|-----------------------------------------|---------------------------------------------------------------------------|--|--|

|                                         | Tien-Fu Chen, National Chung Cheng University,<br>Taiwan                  |  |  |

|                                         | Jihong Kim, Seoul National University, Korea                              |  |  |

|                                         | Kyu Ho Park, Korea Advanced Institute of Science<br>and Technology, Korea |  |  |

|                                         | Guohui Li, Huazhong University of Science and<br>Technology, China        |  |  |

|                                         | Sam Hyuk Noh, Hong-Ik University, Korea                                   |  |  |

|                                         | Stephen A. Edwards, Columbia University, USA                              |  |  |

|                                         | Sree. Rajan, Fujitsu Laboratories of America, USA                         |  |  |

|                                         | Tai-Yi Huang, National Tsing Hua University, Taiwan                       |  |  |

|                                         | Ying-Dar Lin, National Chiao-Tung University,<br>Taiwan                   |  |  |

| Power-Aware                             | X. Sharon Hu, University of Notre Dame, USA                               |  |  |

| Computing                               | Chris Poellabauer, University of Notre Dame, USA                          |  |  |

|                                         | Chi-Ying Tsui, Hong Kong University of Science and                        |  |  |

|                                         | Technology, Hong Kong                                                     |  |  |

|                                         | Tianzhou Chen, Zhejiang University, China                                 |  |  |

|                                         | Gang Quan, University of South Carolina, USA                              |  |  |

|                                         | Joerg Henkel, Univeristy of Karlsruhe, Germany                            |  |  |

|                                         | Kanishka Lahiri, NEC Laboratories America, USA                            |  |  |

|                                         | Luca Benini, University of Bologna, Italy                                 |  |  |

|                                         | Pai Chou, University of California, Irvine, USA                           |  |  |

|                                         | Vijaykrishnan Narayanan, Penn State University, USA                       |  |  |

|                                         | Yung-Hsiang Lu, Purdue University, USA                                    |  |  |

| HW/SW Co-design<br>and Design<br>Automation | <ul><li>Samarjit Chakraborty, National University of<br/>Singapore, Singapore</li><li>Twan Basten, Eindhoven University of Technology,<br/>Nethelands</li><li>Andy Pimentel, University of Amsterdam,</li></ul> |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | Netherlands<br>Aviral Shrivastava, Arizona State University, USA<br>Chi-Ying Tsui, Hong Kong University of Science<br>and Technology, Hong Kong                                                                 |

|                                             | <ul><li>Karam S. Chatha, Arizona State University, USA</li><li>Mathias Gries, Intel Corp., Germany</li><li>M. Balakrishnan, IIT Delhi, India</li><li>Miguel Miranda, IMEC, Belgium</li></ul>                    |

|                                             | Naehyuck Chang, Seoul National University, Korea<br>Soumitra K. Nandy, Indian Institute of Science, India<br>Marco Platzner, University of Paderborn, Germany<br>Christian Plessl, ETH Zurich, Switzerland      |

|                                             | Prabhat Mishra, University of Florida, USA<br>Sri Parameswaran, University of New<br>South Wales, Australia                                                                                                     |

|                                             | Hiroto Yasuura, Kyushu University, Japan<br>Zonghua Gu, Hong Kong University of Science and<br>Technology, Hong Kong                                                                                            |

| Network Protocol                            | Ai-Chung Pang, National Taiwan University, Taiwan<br>Jelena Misic, University of Manitoba, Canada<br>Masayuki Murata, Osaka University, Japan<br>Noel Crespi, GET-INT, France                                   |

|                                             | <ul> <li>Shun-Ren Yang, National Tsing-Hua University,<br/>Taiwan</li> <li>Andreas Terzis, Johns Hopkins University, USA</li> <li>Yang Xiao, University of Alabama, USA</li> </ul>                              |

| Embedded and<br>Reconfigurable Hardware     | Hiroyuki Tomiyama, Nagoya University, Japan<br>Adam Donlin, Xilinx, USA<br>Chia-Tien Dan Lo, University of Texas at San<br>Antonio, USA                                                                         |

|                                             | Elaheh Bozorgzadeh, University of California,<br>Irvine, USA<br>Shinya Honda, Nagoya University, Japan                                                                                                          |

|                                             | Yin-Tsung Hwang, National Yunlin University of<br>Science and Technology, Taiwan                                                                                                                                |

|                                             | Ing-Jer Haung, National Sun Yat-Sen<br>University, Taiwan<br>Koji Inoue, Kyushu University, Japan                                                                                                               |

|                                 | Ki-Seok Chung, Hanyang University, Korea<br>Yuichiro Shibata, Nagasaki University, Japan           |

|---------------------------------|----------------------------------------------------------------------------------------------------|

| Embedded System<br>Software and | Jinsoo Kim, Korea Advanced Institute of Science and<br>Technology, Korea                           |

| Optimization                    | Pete Beckman, Argonne National Laboratory, USA<br>Francois Bodin, IRISA, France                    |

|                                 | Jinsung Cho, Kyung Hee University, Korea                                                           |

|                                 | Chanik Park, Samsung, Electronics, Korea                                                           |

|                                 | Hwansoo Han, Korea Advanced Institute of Science<br>and Technology, Korea                          |

|                                 | Jenq-Kuen Lee, National Tsing-Hua University,<br>Taiwan                                            |

|                                 | Rong-Guey Chang, National Chung-Cheng<br>University, Taiwan                                        |

|                                 | Stephen A. Edwards, Columbia University, USA                                                       |

|                                 | Sungsoo Lim, Kookmin University, Korea                                                             |

|                                 | Yeh-Ching Chung, National Tsing-Hua<br>University, Taiwan                                          |

| Sensor Networks                 | Yu-Chee Tseng, National Chiao-Tung<br>University, Taiwan                                           |

|                                 | Chih-Min Chao, National Taiwan Ocean<br>University, Taiwan                                         |

|                                 | Chien-Chung Shen, University of Delaware, USA                                                      |

|                                 | Hsi-Lu Chao, Naitonal Chiao-Tung<br>University, Taiwan                                             |

|                                 | Hyuncheol Park, Information and Communication                                                      |

|                                 | University, Korea                                                                                  |

|                                 | Chung-Ta King, National Tsing Hua<br>University, Taiwan                                            |

|                                 | Loren Schwiebert, Wayne State University, USA                                                      |

|                                 | Mario Cagalj, University of Split, Croatia                                                         |

|                                 | Ming-Hour Yang, Chung Yuan University, Taiwan                                                      |

|                                 | Sameer S. Tilak, University of California,<br>San Diego                                            |

|                                 | Sandeep Gupta, Arizona State University, USA                                                       |

|                                 | Jang-Ping Sheu, National Central University, Taiwan                                                |

|                                 | Silvia Giordano, University of Applied                                                             |

|                                 | Science - SUPSI, Switzerland                                                                       |

|                                 | Shih-Lin Wu, Chang Gung University, Taiwan                                                         |

|                                 | Wang-Chien Lee, Penn State University, USA                                                         |

|                                 | Yang Yang, University College London, Taiwan<br>Yuh-Shyan Chen, National Taipei University, Taiwan |

| Mobile Computing                   | <ul> <li>Nicolas Navet, INRIA Lorraine, France</li> <li>Ben A. Abderazek, National University of<br/>Electro-communications, Japan</li> <li>Jiannong Cao, Hong Kong Polytechnic University,<br/>Hong Kong</li> <li>Eric Fleury, INRIA-INSA Lyon, France</li> <li>Guoliang Xing, City University of Hong Kong,<br/>Hong Kong</li> <li>Jean-Dominique Decotignie, Centre<br/>Suisse d'Electronique et de Microtechnique,<br/>Switzerland</li> <li>Jiman Hong, Soongsil University, Korea</li> <li>Luis Almeida, University of Aveiro, Portugal</li> <li>Lucia Lo Bello, University of York, UK</li> <li>Simonot-Lion Francoise, LORIA-INPL, France</li> </ul>                                                     |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Agent and Distributed<br>Computing | <ul> <li>I-Ling Yen, University of Texas at Dallas, USA</li> <li>Alessio Bechini, University of Pisa, Italy</li> <li>Ann T. Tai, IA Tech., Inc., USA</li> <li>Ing-Ray Chen, Virginia Tech., USA</li> <li>Kane Kim, UC, Irvin, USA</li> <li>Insup Lee, University of Pennsylvania, USA</li> <li>Yunhao Liu, Hong Kong University of Science and<br/>Technology, Hong Kong</li> <li>Neeraj Mittal, The University of Texas at Dallas,<br/>USA</li> <li>Shangping Ren, Illinois Institute of Technology, USA</li> <li>Jeffrey Tsai, University of Illinois at Chicago, USA</li> <li>Dongfeng Wang, Wind River, USA</li> </ul>                                                                                      |

| Security and Fault<br>Tolerance    | <ul> <li>Jiman Hong, Soongsil University, Korea</li> <li>Jean-Philippe Martin, Microsoft Research, UK</li> <li>Andres Marin, University Carlos III of Madrid, Spain</li> <li>Roberto Di Pietro, University of Rome <ul> <li>La Sapienza, Italy</li> </ul> </li> <li>Zhenhai Duan, Florida State University, USA</li> <li>Geyong Min, University of Bradford, UK</li> <li>Gwangil Jeon, Korea Polytechnic University, Korea</li> <li>Haklin Kimm, East Stroudsburg University of <ul> <li>Pennsylvania, USA</li> </ul> </li> <li>Hung-Chang Hsiao, National Tsing-Hua <ul> <li>University, Taiwan</li> </ul> </li> <li>Heejun Ahn, Seoul National University of <ul> <li>Catalonia, Spain</li> </ul> </li> </ul> |

|                                  | <ul> <li>Junghoon Lee, Cheju National University, Korea</li> <li>Klaus Kursawe, Katholieke Universiteit</li> <li>Leuven, Belgium</li> <li>Madjid Merabti, Liverpool John Moores University,</li> <li>UK</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Marc Lacoste, France Telecom Division R&D, France Emilia Rosti, University of Milan, Italy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                  | <ul><li>Sangjun Lee, Soongsil University, Korea</li><li>Willy Susilo, University of Wollongong, Australia</li><li>Yi Mu, University of Wollongong, Australia</li><li>Yunghsiang S. Han, National Taipei</li><li>University, Taiwan</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                  | Zhaoyu Liu, University of North Carolina at<br>Charlotte, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  | Yingwu Zhu, Seattle University, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Embedded System<br>Architectures | <ul> <li>Dongsheng Wang, Tsinghua University, China</li> <li>Achim Rettberg, University of Paderborn, Germany</li> <li>Guangzuo Cui, Peking University, China</li> <li>Franz Rammig, University of Paderborn, Germany</li> <li>Yunde Jia, Beijing Institute of Technology, China</li> <li>Junzhao Sun, University of Oulu, Finland</li> <li>Mingyu Lu, Dalian Maritime University, China</li> <li>Huadong Ma, Beijing University of Posts and</li> <li>Telecommunications, China</li> <li>Neil Bergmann, The University of Queensland,</li> <li>Australia</li> <li>Roger Woods, Queen's University of Belfast, UK</li> <li>Rajesh Gupta, University of California, USA</li> <li>Ming Xu, National University of Defense</li> <li>Technology, China</li> </ul> |

|                                  | Xiao Zong Yang, Harbin Institute of<br>Technology, China                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                  | Yingfei Dong, University of Hawaii, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                  | Zoran Salcic, University of Auckland, New Zealand<br>Zhimin Zhang, Chinese Academy of Sciences, China                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Middleware and P2P               | Cho-Li Wang, University of Hong Kong, Hong Kong<br>Bo Hong, Drexel University, USA<br>Ching-Hsien Hsu, Chung Hua University, Taiwan<br>Bin Xiao, Hong Kong Polytechnic University,<br>Hong Kong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  | Jemal Abbawajy, Deakin University, Australia<br>Kuan-Ching Li, Providence University, Taiwan<br>Zhiling Lan, Illinois Institute of Technology, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                 | <ul> <li>Yunhao Liu, Hong Kong University of Science and<br/>Technology, Hong Kong</li> <li>Yuanchun Shi, Tsinghua University, China</li> <li>Young-Sik Jeong, Wonkwang University, Korea</li> <li>Weisong Shi, Wayne State University, USA</li> <li>Zhaohui Wu, Zhejiang University, China</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multimedia, Human-<br>Computer Interface<br>and Data Management | <ul> <li>Joseph Ng, Hong Kong Baptist University,<br/>Hong Kong</li> <li>Leonard Barolli, Fukuoka Institute of Technology,<br/>Japan</li> <li>Jong Hyuk Park, R&amp;D Institute in Hanwha S&amp;C<br/>Co., Ltd., Korea</li> <li>Clement Leung, Victoria University, Australia</li> <li>Reynold Cheng, Hong Kong Polytechnic<br/>University, Hong Kong</li> <li>Victor Lee, City University of Hong Kong,<br/>Hong Kong</li> <li>David Tanier, Monash University, Australia</li> <li>Kazunori Takashio, Keio University, Japan</li> <li>Hidenori Nakazato, Waseda University, Japan</li> <li>Seongsoo Hong, Seoul National University, Korea</li> <li>Tatsuo Nakajima, Waseda University, Taiwan</li> <li>Jianliang Xu, Hong-Kong Baptist University,<br/>Hong Kong</li> </ul> |

| Wireless Networks                                               | <ul> <li>Mohan Kumar, University of Texas at Arlington, USA</li> <li>Giusseppe Anastasi, University of Pisa, Italy</li> <li>Manimaran Govindarasu, Iowa State University, USA</li> <li>Kwan-Wu Chin, Wollongong University, Australia</li> <li>Mijeom Kim, Korea Telecom, Korea</li> <li>Nallasamy Mani, Monash University, Australia</li> <li>Stephan Olariu, Old Dominion University, USA</li> <li>Cristina Pinotti, University of Perugia, Italy</li> <li>Swaroop Kalasapur, Samsung Research, USA</li> <li>Sieteng Soh, Curtin University of Technology, Australia</li> <li>Yonghe Liu, University of Texas at Arlington, USA</li> </ul>                                                                                                                                  |

| Main Track                                                      | Tei-Wei Kuo, National Taiwan University, Taiwan<br>Chih-Yuan Huang, Silicon Integrated Systems<br>Corp., Taiwan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Young-Sik Jeong, Wonkwang University, Korea Bernd Kleinjohann, University of Paderborn, Germany Chin-Fu Kuo, National University of Kaohsiung, Taiwan Chi-Sheng Shih, National Taiwan University, Taiwan Zili Shao, Hong Kong Polytech University, Hong Kong Chih-Wen Hsueh, National Taiwan University, Taiwan Doohyun Kim, Konkuk University, Korea Shih-Hao Hung, National Taiwan University, Taiwan Ken-ichi Itoh, Siebold University of Nagasaki, Japan Jen-Wei Hsieh, National Chiavi University, Taiwan Jun Wu, National Pingtung Institute of Commerce, Taiwan Jianwu Zhang, Hangzhou Dianzi University, China Lung-Jen Wang, National Pingtung Institute of Commerce, Taiwan Nei-Chiung Perng, Genesys Logic, Taiwan Shi-Wu Lo, National Chung-Cheng University, Taiwan Ting-Ao Tang, Fudan University, China Tai-Yi Huang, National Tsing Hua University, Taiwan Xiaoyang Zeng, Fudan University, China Chia-Lin Yang, National Taiwan University, Taiwan Cheng-Zhong Xu, Wayne State University, USA Dakai Zhu, University of Texas at San Antonio, USA

# Table of Contents

### Power Aware Computing

| Real-Time Loop Scheduling with Energy Optimization Via DVS and ABB for Multi-core Embedded System                              | 1  |

|--------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                |    |

| A Software Framework for Energy and Performance Tradeoff in<br>Fixed-Priority Hard Real-Time Embedded Systems                  | 13 |

|                                                                                                                                |    |

| A Shortest Time First Scheduling Mechanism for Reducing the Total<br>Power Consumptions of an IEEE 802.11 Multiple Rate Ad Hoc |    |

| Network                                                                                                                        | 25 |

| Energy Efficient Scheduling for Real-Time Systems with Mixed                                                                   |    |

| Workload                                                                                                                       | 33 |

# Reconfigurable Embedded Systems

| Function-Level Multitasking Interface Design in an Embedded<br>Operating System with Reconfigurable Hardware | 45 |

|--------------------------------------------------------------------------------------------------------------|----|

|                                                                                                              |    |

|                                                                                                              |    |

| Task Scheduling for Context Minimization in Dynamically         Reconfigurable Platforms                     | 55 |

| Compiler Support for Dynamic Pipeline Scaling                                                                | 64 |

| Parallel Network Intrusion Detection on Reconfigurable Platforms                                             | 75 |

#### Wireless Networks

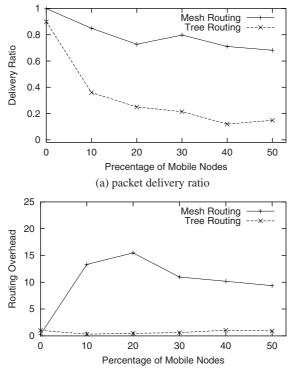

| Evaluating Mobility Support in ZigBee Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| a set as a set of the |    |

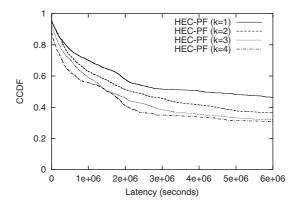

| On Using Probabilistic Forwarding to Improve HEC-Based Data<br>Forwarding in Opportunistic Networks | 101 |

|-----------------------------------------------------------------------------------------------------|-----|

|                                                                                                     |     |

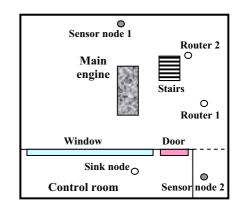

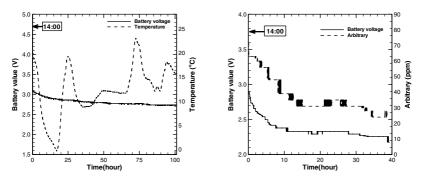

| Employment of Wireless Sensor Networks for Full-Scale Ship<br>Application                           | 113 |

| and the subject the second second                                                                   |     |

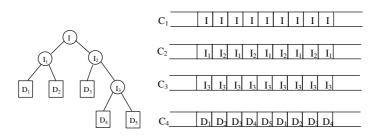

| Improving the Performance of the Wireless Data Broadcast by the Cyclic Indexing Schemes             | 123 |

#### Real-Time/Embedded Operating Systems

| Revisiting Fixed Priority Techniques                                                                    | 134 |

|---------------------------------------------------------------------------------------------------------|-----|

|                                                                                                         |     |

| A Server-Side Pre-linking Mechanism for Updating Embedded Clients<br>Dynamically                        | 146 |

| Real-Time Scheduling Under Time-Interval Constraints                                                    | 158 |

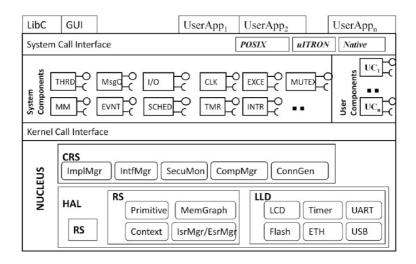

| Towards a Software Framework for Building Highly Flexible<br>Component-Based Embedded Operating Systems | 170 |

## Embedded System Architectures

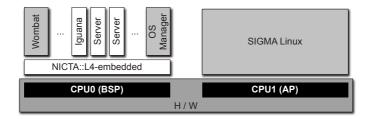

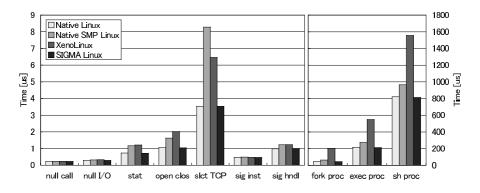

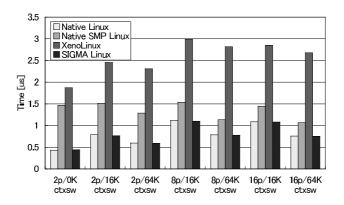

| A Study on Asymmetric Operating Systems on Symmetric<br>Multiprocessors                                         | 182 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| an shekara ya kata kata kata ya kata kata kata ka                                                               |     |

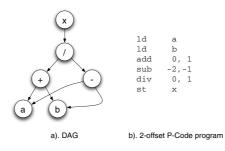

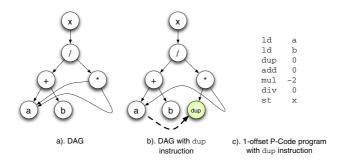

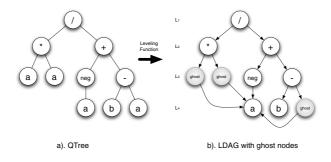

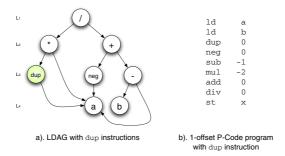

| An Efficient Code Generation Algorithm for Code Size Reduction<br>Using 1-Offset P-Code Queue Computation Model | 196 |

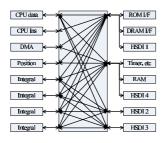

| Interconnection Synthesis of MPSoC Architecture for Gamma<br>Cameras                                            | 209 |

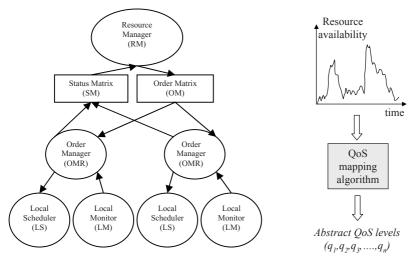

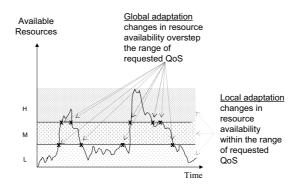

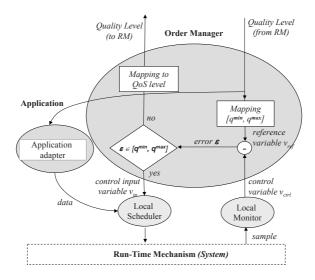

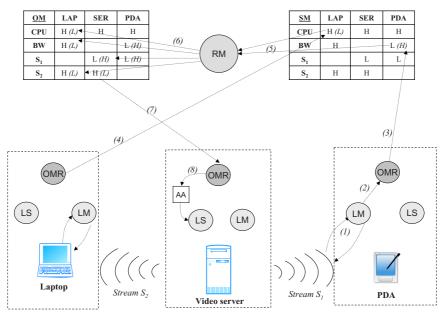

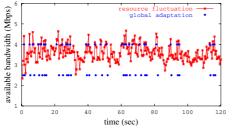

| Integrated Global and Local Quality-of-Service Adaptation in<br>Distributed, Heterogeneous Systems              | 219 |

# Scheduling and Resource Management

| Toward to Utilize the Heterogeneous Multiple Processors of the Chip<br>Multiprocessor Architecture         | 234 |

|------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                            |     |

| Consensus-Driven Distributable Thread Scheduling in Networked<br>Embedded Systems                          | 247 |

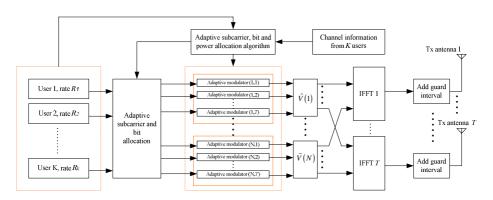

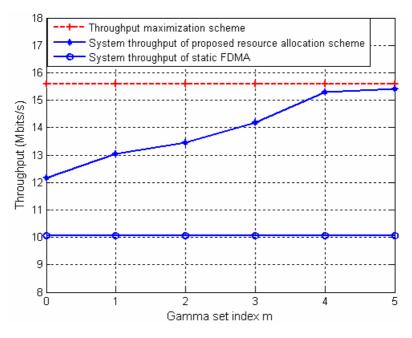

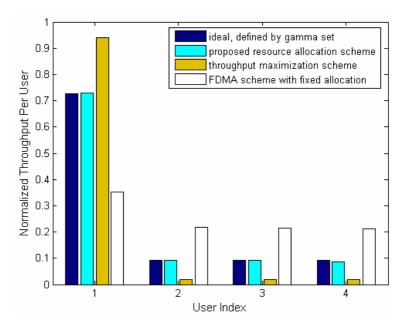

| Novel Radio Resource Management Scheme with Low Complexity for<br>Multiple Antenna Wireless Network System | 261 |

# Mobile Computing

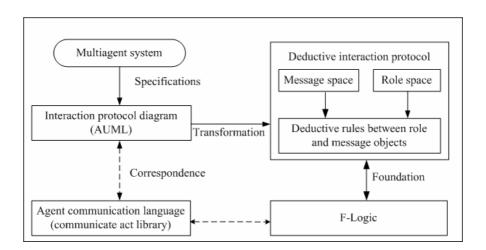

| Modelling Protocols for Multiagent Interaction by F-logic        | 271 |

|------------------------------------------------------------------|-----|

|                                                                  |     |

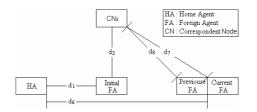

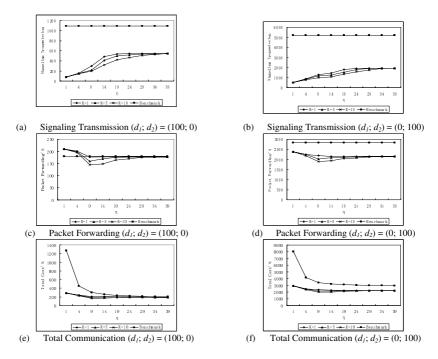

| Adding Adaptability to Mailbox-Based Mobile IP                   | 283 |

|                                                                  |     |

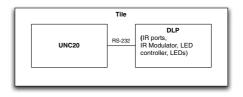

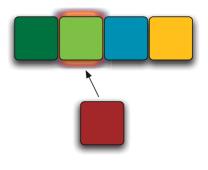

| Palpability Support Demonstrated                                 | 294 |

|                                                                  |     |

| GPS-Based Location Extraction and Presence Management for Mobile |     |

| Instant Messenger                                                | 309 |

| · · · · · · · · · · · · · · · · · · ·                            |     |

# System Security

| Bilateration: An Attack-Resistant Localization Algorithm of Wireless<br>Sensor Network | 321 |

|----------------------------------------------------------------------------------------|-----|

|                                                                                        |     |

| ID-Based Key Agreement with Anonymity for Ad Hoc Networks                              | 333 |

|                                                                                        |     |

| Buffer Cache Level Encryption for Embedded Secure Operating<br>System                  | 346 |

|                                                                                        |     |

|                                                                                        |     |

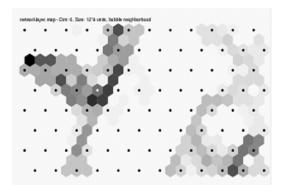

| SOM-Based Anomaly Intrusion Detection System                                           | 356 |

|                                                                                        |     |

# **Networks Protocols**

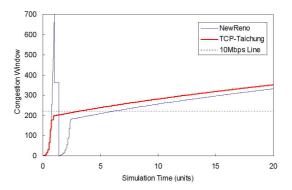

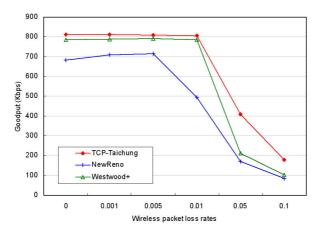

| TCP-Taichung: A RTT-Based Predictive Bandwidth Based with<br>Optimal Shrink Factor for TCP Congestion Control in Heterogeneous<br>Wired and Wireless Networks | 367 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

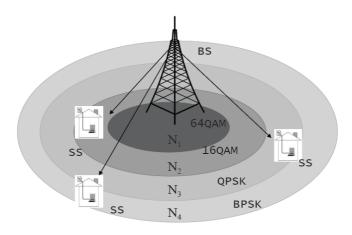

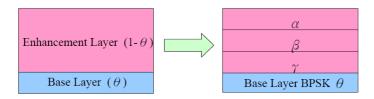

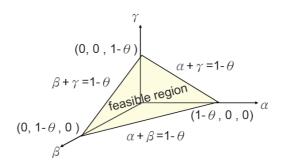

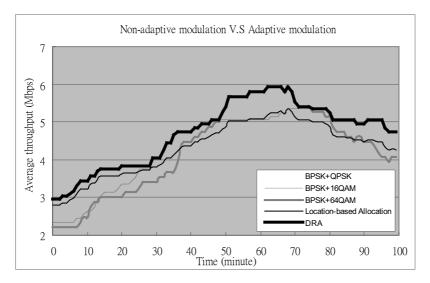

| Dynamic Rate Adjustment (DRA) Algorithm for WiMAX Systems<br>Supporting Multicast Video Services                                                              | 379 |

| Efficient and Load-Balance Overlay Multicast Scheme with Path<br>Diversity for Video Streaming                                                                | 389 |

| A Cross Layer Time Slot Reservation Protocol for Wireless Networks                                                                                            | 400 |

# Fault Tolerance

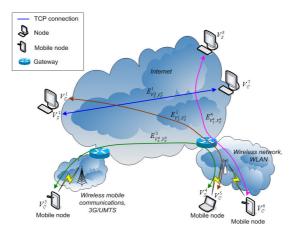

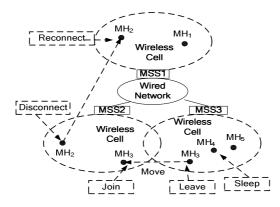

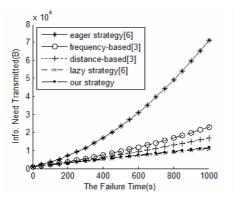

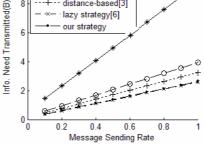

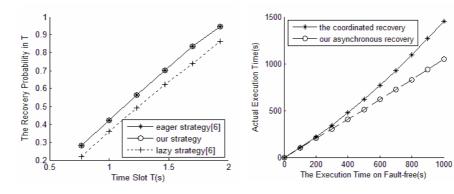

| An Efficient Handoff Strategy for Mobile Computing Checkpoint<br>System                                          | 410 |

|------------------------------------------------------------------------------------------------------------------|-----|

| and the second |     |

| A Lightweight RFID Protocol Using Substring                                                                      | 422 |

|                                                                                                                  |     |

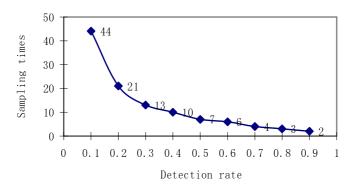

| The Reliability of Detection in Wireless Sensor Networks: Modeling<br>and Analyzing                              | 432 |

|                                                                                                                  |     |

|                                                                                                                  |     |

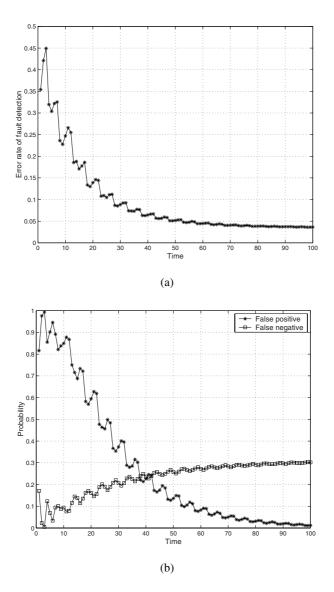

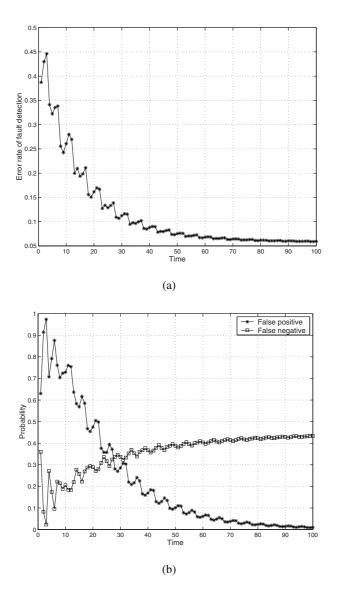

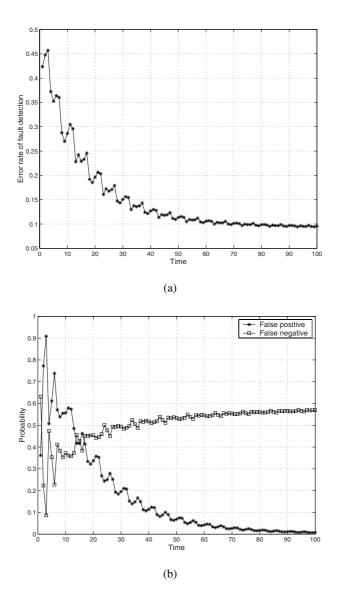

| Fast and Simple On-Line Sensor Fault Detection Scheme for Wireless      Sensor Networks                          | 444 |

| in the state of the second state of the state of the second state of the second state of the second state of the |     |

#### Human-Computer Interface and Data Management

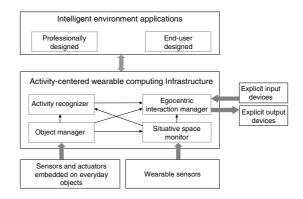

| An Activity-Centered Wearable Computing Infrastructure for<br>Intelligent Environment Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 456 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Finding and Extracting Data Records from Web Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 466 |

| and y types any second strain a pression of the second strains and the second strains of the second strains strains of the second st |     |

| Towards Transparent Personal Content Storage in Multi-service Access |     |

|----------------------------------------------------------------------|-----|

| Networks                                                             | 479 |

|                                                                      |     |

|                                                                      |     |

| Extraction and Classification of User Behavior                       | 493 |

| · · · · · · · · · · · · · · · · · · ·                                |     |

#### HW/SW Co-design and Design Automations

| A Floorplan-Based Power Network Analysis Methodology for<br>System-on-Chip Designs                           | 507 |

|--------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                              |     |

| A Multi Variable Optimization Approach for the Design of Integrated<br>Dependable Real-Time Embedded Systems | 517 |

|                                                                                                              |     |

| SystemC-Based Design Space Exploration of a 3D Graphics<br>Acceleration SoC for Consumer Electronics         | 531 |

| Optimal Allocation of I/O Device Parameters in Hardware and<br>Software Codesign Methodology                 | 541 |

|                                                                                                              |     |

# Service-Aware Computing

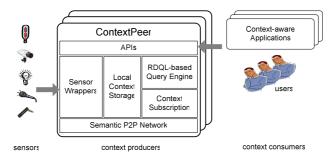

| A Semantic P2P Framework for Building Context-Aware Applications<br>in Multiple Smart Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 553 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Usage-Aware Search in Peer-to-Peer Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 565 |

| and a first and a second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

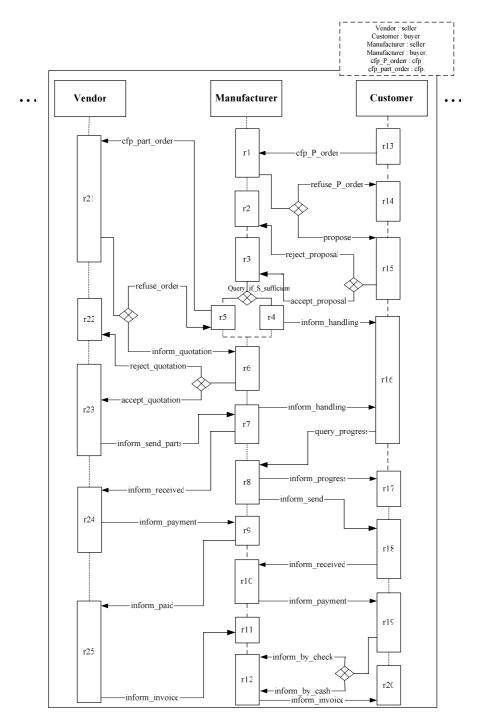

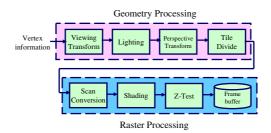

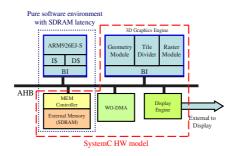

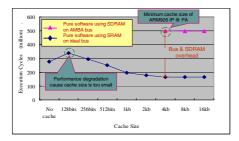

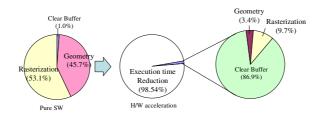

| A Service Query Dissemination Algorithm for Accommodating<br>Sophisticated QoS Requirements in a Service Discovery System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 577 |